# 5.0" 720 x 1280 **High brightness color TFT-LCD module**

Model: VM05B4 VN

Date: Jul. 16th, 2021

Version: 01

Note: This specification is subject to change without notice

| Customer : |          |

|------------|----------|

|            | Date :   |

| Approved   | Prepared |

| Date:      | Date:    |

MODEL:VM05B4 VN Page: 1/21 Doc. No: Preliminary

# **Contents**

- 1. Handling Precautions

- 2. General Description

- 2.1 Overview

- 2.2 Features

- 2.3 Application

- 2.4 Display specifications

- 2.5 Optical characteristics

- 3. Absolute Maximum Ratings

- 3.1 TFT LCD module

- 3.2 Backlight unit

- 3.3 Environment

#### 4. Electrical characteristics

- 4.1 LCD electronics specification

- 4.2 Backlight unit

- 4.3 Interface connector

- 4.3.1 TFT connector(CN1)

# 5. Signal characteristics

- 5.1 LP mode

- 5.2 High speed mode

- 5.3 Low power mode

- 5.4 DSI bursts mode

- 6. Reset timing

- 7. Reliability Test

- 8. Shipping package

- 9. Mechanical Characteristics

# RECORD OF REVISION

| Version and Date                 | Page | Old description                            | New description | Remark |

|----------------------------------|------|--------------------------------------------|-----------------|--------|

| Version and Date  0.1 2021/07/16 | Page | Old description First Edition for customer | New description | Remark |

|                                  |      |                                            |                 |        |

MODEL:VM05B4 VN Page: 3/21 Doc. No: Preliminary

# 1. Handling Precautions

- 1) Since front polarizer is easily damaged, pay attention not to scratch it.

- 2) Be sure to turn off power supply when inserting or disconnecting from input connector.

- 3) Wipe off water drop immediately. Long contact with water may cause discoloration or spots.

- 4) When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth.

- 5) Since the panel is made of glass, it may break or crack if dropped or bumped on hard

- 6) Since CMOS LSI is used in this module, take care of static electricity and insure human earth when handling.

- 7) Do not open or modify the Module Assembly.

- 8) Do not press the reflector sheet at the back of the module to any directions.

- 9) At the insertion or removal of the Signal Interface Connector, be sure not to rotate nor tilt the Interface Connector of the TFT Module.

- 10) After installation of the TFT Module into an enclosure, do not twist nor bend the TFT Module even momentary. At designing the enclosure, it should be taken into consideration that no bending/twisting forces are applied to the TFT Module from outside. Otherwise the TFT Module may be damaged.

MODEL:VM05B4 VN Page: 4/21 Doc. No: **Preliminary**

# 2. General Description

#### 2.1 Overview

This specification applies to the Color Active Matrix Liquid Crystal Display composed of a TFT-LCD display a LED backlight system. The screen format is intended to support 720(H) x 1280(V) screen.

#### 2.2 Features

- High brightness display by LED backlight.

- Long operation lifetime BLU design

- mipi interface

- Wide view angle

- Wide operation temperature

- RoHS Compliance

#### 2.3 Application

Industrial applications.

Page: 5/21 Doc. No: MODEL:VM05B4 VN Preliminary

# 2.4 Display specifications

| Items                      | Unit              | Specification                        |

|----------------------------|-------------------|--------------------------------------|

| Screen Diagonal            | inch              | 4.98"                                |

| Active Area                | mm                | 62.1 (H) X 110.4 (V)                 |

| Pixels H x V               | pixels            | 720 x3(RGB) x 1280                   |

| Pixels Pitch               | um                | 86.25 (per one triad) x 86.25        |

| Pixel Arrangement          |                   | RGB Vertical stripe                  |

| Display mode               |                   | Normally black                       |

| White luminance (center)   | Cd/m <sup>2</sup> | 480 (Typ)                            |

| Contrast ratio             |                   | 800:1 (Typ.)                         |

| Optical Response Time      | msec              | 20 ms (Typ. On/off)                  |

| Normal Input Voltage VDD   | Volt              | 2.8                                  |

| Power Consumption          | Watt              | TBD                                  |

| (Vcc Line + LED backlight) |                   | (VDD line=TBD; LED lines= 0.896 W)   |

| Weight                     | Grams             | TBD                                  |

| Physical size              | mm                | 65.3 (W)× 119.3 (H)× 1.73 (D, w PCB) |

| Electrical Interface       |                   | MIPI (2Lane)                         |

| Driver IC                  |                   | ILI9881D                             |

| Temperature range          |                   |                                      |

| Operating                  | °C                | -20 ~ 70 (TFT surface)               |

| Storage                    | °C                | -30 ~ 80                             |

| RoHS Compliance            |                   | RoHS Compliance                      |

MODEL:VM05B4 VN Page: 6/21 Doc. No: Preliminary

# 2.5 Optical characteristics

The following optical characteristics are measured under stable condition at 25 °C

| Items                | Unit              | Conditions         | Min.  | Тур.  | Max.  | Note |

|----------------------|-------------------|--------------------|-------|-------|-------|------|

|                      |                   | Horizontal (Right) |       | 80    |       |      |

| Viewing angle        | Dog               | CR=10 (Left)       |       | 80    |       | 2    |

| viewing angle        | Deg.              | Vertical (Up)      |       | 80    |       | 2    |

|                      |                   | CR=10 (Down)       |       | 80    |       |      |

| Contrast Ratio       |                   | Normal Direction   | 640   | 800   |       | 3    |

| Response Time        | msec              | Raising + Falling  |       | 20    | 25    | 4    |

|                      |                   | Red x              |       | 0.654 |       |      |

|                      |                   | Red y              |       | 0.319 |       |      |

| Color / Chromaticity |                   | Green x            |       | 0.259 |       |      |

| Coordinates (CIE)    |                   | Green y            | -0.05 | 0.574 | +0.05 | 5    |

|                      |                   | Blue x             | -0.05 | 0.140 | +0.05 | 5    |

|                      |                   | Blue y             |       | 0.084 |       |      |

| Color coordinates    |                   | White x            |       | 0.310 |       |      |

| (CIE) White          |                   | White y            |       | 0.329 |       |      |

| Center Luminance     | Cd/m <sup>2</sup> |                    |       | 480   |       | 6    |

| Luminance Uniformity | %                 |                    | 70    | 75    |       | 7    |

| Crosstalk (in 60 Hz) | %                 |                    |       |       | 1.5   |      |

| Flicker              | dB                |                    |       |       | -20   |      |

Preliminary MODEL:VM05B4 VN Page: 7/21 Doc. No:

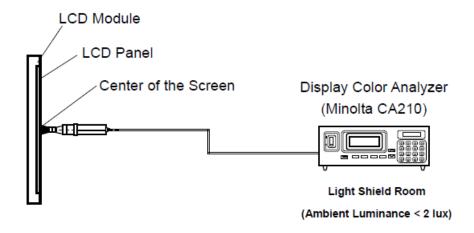

#### Note 1: Measurement method

The LCD module should be stabilized at given temperature for 0.5 hour to avoid abrupt temperature change during measuring. In order to stabilize the luminance, the measurement should be executed after lighting Backlight for 1 hour in a windless room.

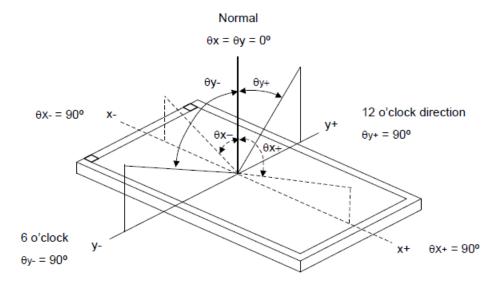

Note 2: Definition of viewing angle

Note 3: Contrast ratio is measured by Minolta CA210

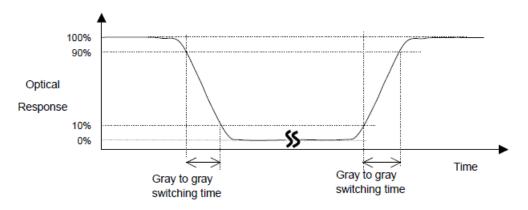

#### Note 4: Definition of Response time

The output signals of photo detector are measured when the input signals are changed from "Full Black" to "Full White" (rising time), and from "Full White" to "Full Black" (falling time), respectively. The response time is interval between the 10% and 90% of amplitudes. Please refer to the figure as below.

Note 5: Color chromaticity and coordinates (CIE) is measured by Minolta CA210

Note 6: Center luminance is measured by Minolta CA210

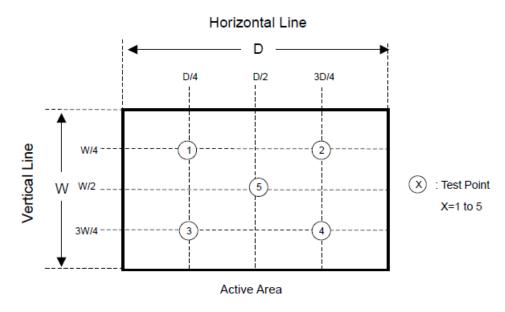

Note 7: Luminance uniformity of these 5 points is defined as below and measured by Minolta CA210

Uniformity = (Min. Luminance of 5 points) / (Max. Luminance of 5 points)

MODEL:VM05B4 VN Page: 9/21 Doc. No: **Preliminary**

# 3. Absolute Maximum Ratings

Absolute maximum ratings of the module are as following:

#### 3.1 TFT LCD module

| Items                  | Symbol            | Min  | Max | Unit | Conditions |

|------------------------|-------------------|------|-----|------|------------|

| Power supply voltage 1 | Vcc               | -0.3 | 6.5 | Volt | Note 1, 2  |

| Power supply voltage 2 | IOV <sub>CC</sub> | -0.3 | 5.5 | Volt |            |

### 3.2 Backlight unit

| Items                 | Symbol | Min | Max | Unit | Conditions |

|-----------------------|--------|-----|-----|------|------------|

| LED bar input current |        |     | 50  | mA   |            |

#### 3.3 Environment

| Items                 | Symbol          | Values |      |      | Unit  | Conditions |  |

|-----------------------|-----------------|--------|------|------|-------|------------|--|

|                       | Symbol          | Min.   | Тур. | Max. | Offic | Conditions |  |

| Operation temperature | Tos             | -20    | -    | 70   | οС    |            |  |

| Operation Humidity    | H <sub>OP</sub> | 10     |      | 85   | %     | Note 3     |  |

| Storage temperature   | T <sub>ST</sub> | -30    |      | 80   | οС    | Note 3     |  |

| Storage Humidity      | H <sub>ST</sub> | 5      |      | 90   | %     |            |  |

Note 1: With in Ta= 25°C

Note 2: Permanent damage to the device may occur if exceed maximum values

Note 3: For quality performance, please refer to IIS (Incoming Inspection Standard).

MODEL:VM05B4 VN Page: 10/21 Doc. No: Preliminary

# 4. Electrical characteristics

4.1 LCD electronics specification

AGND = GND = 0V, Ta =  $25^{\circ}$ C

| Parameter                         | Symbol          | Min       | Тур | Max       | Unit |

|-----------------------------------|-----------------|-----------|-----|-----------|------|

| Supply voltage for analog circuit | VCC             | 2.5       | 2.8 | 3.3       | V    |

| Supply voltage for logic circuit  | IOVCC           | 1.65      | 1.8 | 2.0       | V    |

| Input voltage 'H'level            | V <sub>IH</sub> | 0.7*IOVCC | _   | IOVCC     | V    |

| Input voltage 'L'level            | VIL             | GND       | _   | 0.3*IOVCC | V    |

| Output voltage 'H'level           | Vон             | 0.8*IOVCC | _   | IOVCC     | V    |

| Output voltage 'L'level           | V <sub>OL</sub> | GND       | _   | 0.2*IOVCC | V    |

Preliminary MODEL:VM05B4 VN Page: 11/21 Doc. No:

# 4.2 Backlight unit

| Parameter            | Min    | Тур   | Max | Unit   | Note |

|----------------------|--------|-------|-----|--------|------|

| LED voltage (VL)     |        | 22.4  |     | [V]    | 2    |

| LED current (IL)     |        | 40    |     | [mA]   | 2    |

| LED power (PL)       |        | 0.896 |     | [W]    |      |

| LED lite time (MTBF) | 20,000 |       |     | [Hour] | 1    |

Note 1: The "LED lift time" is defined as the module brightness decrease to 50% original brightness that the ambient

Note 2: The variance of LED Light Bar power consumption is  $\pm 10\%$ . Calculator value for reference (IL  $\times$  VL = PLED)

Preliminary MODEL:VM05B4 VN Page: 12/21 Doc. No:

#### 4.3 Interface connector

# 4.3.1 TFT connector(CN1)

| Pin No. | Symbol    | Description                                      |

|---------|-----------|--------------------------------------------------|

| 1       | GND       | Power ground                                     |

| 2       | TOUCH_3V3 | CTP-Power supply                                 |

| 3       | GND       | Power ground                                     |

| 4       | TOUCH_INT | CTP-INT                                          |

| 5       | TOUCH_RST | CTP-Reset signal                                 |

| 6       | TOUCH_SDA | CTP-SDA                                          |

| 7       | TOUCH_SCL | CTP-SCL                                          |

| 8       | GND       | Power ground                                     |

| 9       | LEDK      | LED backlight cathode                            |

| 10      | LEDA      | LED backlight anode                              |

| 11      | ID        | LCM-ID signal                                    |

| 12      | RSTN      | Reset signal(low active)                         |

| 13      | NC        | NC                                               |

| 14      | IOVCC3V3  | Power supply for the logic power and I/O circuit |

| 15      | VCC3V3    | Power supply for the analog power                |

| 16      | GND       | Power ground                                     |

| 17      | NC        | NC                                               |

| 18      | NC        | NC                                               |

| 19      | GND       | Power ground                                     |

| 20      | NC        | NC                                               |

| 21      | NC        | NC                                               |

| 22      | GND       | Power ground                                     |

| 23      | CKP       | MIPI-DSI clock posivtve input pin                |

| 24      | CKN       | MIPI-DSI clock negtive input pin                 |

| 25      | GND       | Power ground                                     |

| 26      | D1P       | MIPI-DSI data lane 1 posivtve input pin          |

| 27      | D1N       | MIPI-DSI data lane 1 negtive input pin           |

| 28      | GND       | Power ground                                     |

| 29      | D0P       | MIPI-DSI data lane 0 posivtve input pin          |

| 30      | D0N       | MIPI-DSI data lane 0 negtive input pin           |

| 31      | GND       | Power ground                                     |

MODEL:VM05B4 VN Page: 13/21 Doc. No: Preliminary

# 5. Signal characteristics

#### 5.1 LP mode

|                                 |                   |                       | ,    |      |      |      |

|---------------------------------|-------------------|-----------------------|------|------|------|------|

| Parameter                       | Symbol Conditions |                       |      | Unit |      |      |

| Parameter                       | Symbol            | Conditions            | Min. | Тур. | Max. | Unit |

| Logic high level input voltage  | VIHLPCD           | LP-CD                 | 450  | -    | 1350 | mV   |

| Logic low level input voltage   | VILLPCD           | LP-CD                 | 0    | -    | 200  | mV   |

| Logic high level input voltage  | VIHLPRX           | LP-RX(CLK, D0)        | 880  | -    | 1350 | mV   |

| Logic low level input voltage   | VILLPRX           | LP-RX(CLK, D0)        | 0    | -    | 550  | mV   |

| Logic low level input voltage   | VILLPRXULP        | LP-RX(CLK ULP mode)   | 0    | -    | 300  | mV   |

| Logic high level output voltage | VOHLPTX           | LP-TX(D0)             | 1.1  | -    | 1.3  | V    |

| Logic low level output voltage  | VOLLPTX           | LP-TX(D0)             | -50  | -    | 50   | mV   |

| Logic high level input current  | VIH               | LP-CD, LP-RX          | -    | -    | 10   | uA   |

| Logic low level input current   | VIL               | LP-CD, LP-RX          | -10  | -    | -    | uA   |

| Input pulse rejection           | SGD               | DSI-CLK+/-, DSI-D0+/1 | -    | -    | 300  | Vps  |

Input glitch rejections of low-power receivers

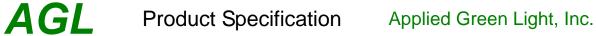

### 5.2 High speed mode

| Parameter                                             | Symbol                | Conditions                       |     | Spec. |      | Unit |

|-------------------------------------------------------|-----------------------|----------------------------------|-----|-------|------|------|

|                                                       | Symbol                | Symbol Conditions                |     | Typ.  | Max. | Unit |

| Input common mode                                     | Vcmclk<br>Vcmdata     | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | 70  | -     | 330  | mV   |

| Input common mode variation<br><450 MHZ               | VCMRCLKL<br>VCMRDATAL | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -50 | -     | 50   | mV   |

| Input common mode variation<br>>450 MHZ               | VCMRCLKM<br>VCMRDATAM | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -   | -     | 100  | mV   |

| Low-level differential Input threshold                | VTHLCLK<br>VTHLDATA   | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -70 | -     | -    | mV   |

| High-level differential Input threshold               | VTHHCLK<br>VTHHDATA   | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -   | -     | 70   | mV   |

| Single ended input low voltage                        | VILHS                 | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -40 | -     | -    | mV   |

| Single ended input high voltage                       | VIHHS                 | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -   | -     | 460  | mV   |

| Differential input termination resistor               | RTERM                 | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | 80  | 100   | 125  | Ω    |

| Single-ended threshold voltage for termination enable | VTERMEN               | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -   | -     | 450  | mV   |

| Termination capacitor                                 | Степм                 | DSI_CP/DSI_CN<br>DSI_D0P/DSI_D0P | -   | -     | -    | pF   |

Differential voltage range and Command mode voltage

MODEL:VM05B4 VN Doc. No: Page: 14/21 Preliminary

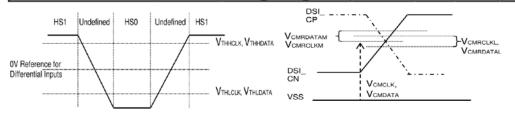

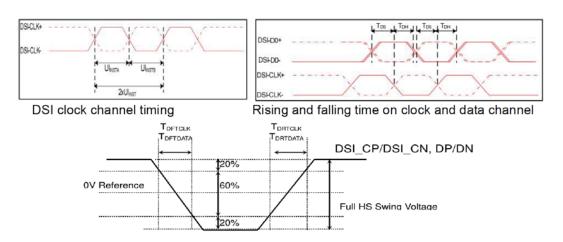

Rising and falling time on clock and data channel

|         | $(VSSA=0V, IOVCC=1.65V \text{ to } 3.3V, VCI=2.5V \text{ to } 3.3V, T_A = -30 \text{ to } 70^{\circ}C)$ |                      |         |      |       |      |  |  |

|---------|---------------------------------------------------------------------------------------------------------|----------------------|---------|------|-------|------|--|--|

| Signal  | Item                                                                                                    | Symbol               |         | Unit |       |      |  |  |

| Signal  |                                                                                                         |                      | Min.    | Тур. | Max.  | Onit |  |  |

| DSI CP/ | Double UI instantaneous                                                                                 | 2xUINST              | TBD     | -    | 25    | ns   |  |  |

| DSI_CP/ | UI instantaneous                                                                                        | UINSTA               | TBD -   | 12.5 | ns    |      |  |  |

| DSI_CIV |                                                                                                         | UINSTB               |         | -    | 12.5  | 115  |  |  |

| DP/DN   | Data to clock setup time                                                                                | T <sub>DS</sub>      | 0.15xUI | -    | -     | ps   |  |  |

| DF/DIN  | Data to clock hold time                                                                                 | T <sub>DH</sub>      | 0.15xUI | -    | -     | ps   |  |  |

| DSI_CP/ | Differential rise time for clock                                                                        | TDRTCLK              | 150     | -    | 0.3UI | ps   |  |  |

| DSI_CN  | Differential fall time for clock                                                                        | TDFTCLK              | 150     | -    | 0.3UI | ps   |  |  |

| DP/DN   | Differential rise time for data                                                                         | T <sub>DRTDATA</sub> | 150     | -    | 0.3UI | ps   |  |  |

| DF/DIN  | Differential fall time for data                                                                         | T <sub>DFTDATA</sub> | 150     | -    | 0.3UI | ps   |  |  |

High Speed Mode Timing Characteristics

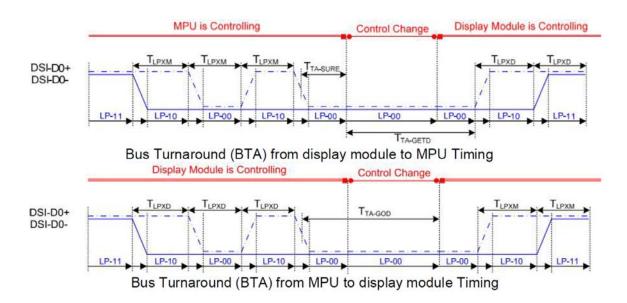

#### 5.3 Low power mode

MODEL:VM05B4 VN Page: 15/21 Doc. No: Preliminary

(VSSA=0V, IOVCC=1.65V to 2.0V, VCI=2.3V to 3.3V,TA = -30 to 70°C)

| Signal              | Item                                                   | Symbol               | Spec.   |      |         | Unit  |

|---------------------|--------------------------------------------------------|----------------------|---------|------|---------|-------|

| Signal              | item                                                   | Syllibol             | Min.    | Тур. | Max.    | Oilit |

| DSI_D0P/<br>DSI_D0P | Length of LP-00/LP01/LP10/LP11<br>Host→ Display module | Тьрхм                | 50      | -    | -       | ns    |

|                     | Length of LP-00/LP01/LP10/LP11 Display module →Host    | TLPXD                | 50      | -    | -       | ns    |

|                     | Time-out before the MPU start driver                   | T <sub>TA-SURE</sub> | TLPXD   | -    | 2xTLPXD | ns    |

|                     | Time to drive LP-00 by display module                  | T <sub>TA-GET</sub>  | 5xTlpxd | -    | -       | ns    |

|                     | Time to drive LP-00 after turnaround request Host      | T <sub>TAGO</sub>    | 4xTLPXD | -    | -       | ns    |

**DSI Low Power Mode Characteristics**

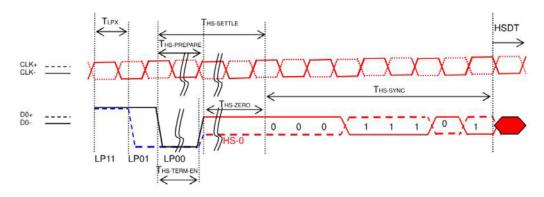

#### 5.4 DSI bursts mode

| Signal              | Item                                                | Cumbal              | Spec.   |      |         | Unit |  |

|---------------------|-----------------------------------------------------|---------------------|---------|------|---------|------|--|

| Signal              | item                                                | Symbol              | Min.    | Тур. | Max.    | Onit |  |

|                     | Length of LP-00/LP01/LP10/LP11                      | TLPX                | 50      | -    | -       | ns   |  |

| DSI_D0P/<br>DSI_D0P | Time to Driver LP-00 to prepare for HS transmission | THS-PREPARE         | 40+4UI  | -    | 85+6UI  | ns   |  |

|                     | Time to enable data receiver line termination       | THS-TERM-EN         | -       | -    | 35+4xUI | ns   |  |

|                     | Time to drive LP-00 by display module               | T <sub>TA-GET</sub> | 5xTLPXD | -    | -       | ns   |  |

|                     | Time to drive LP-00 after turnaround request Host   | T <sub>TAGO</sub>   | 4xTLPXD | -    | -       | ns   |  |

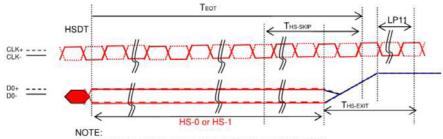

DSI Low Power Mode to/from High Speed Mode Timing

If the last bit is HS-0, the transmitter changes from HS-0 to HS-1 If the last bit is HS-0, the transmitter changes from HS-1 to HS-0

MODEL:VM05B4 VN Page: 16/21 Doc. No: Preliminary

| Signal              | Itam                                                             | Cumbal   | Spec. |      |         | I I mid |

|---------------------|------------------------------------------------------------------|----------|-------|------|---------|---------|

| Signai              | Item                                                             | Symbol   | Min.  | Typ. | Max.    | Unit    |

| DSI_D0P/<br>DSI_D0P | Time-Out at Display Module to Ignore<br>Transition Period of EoT | THS-SKIP | 40    | -    | 55+4xUI | ns      |

| D31_D0P             | Time to Driver LP-11 after HS Burst                              | THS-EXIT | 100   | -    | -       | ns      |

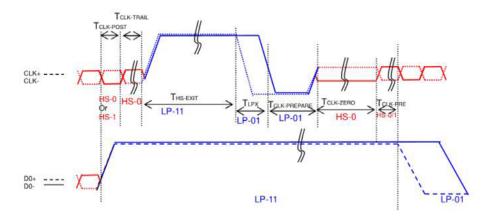

DSI Low Power Mode to High Speed Mode Timing

| Cimmal  | lt                                                                                                                          | C                           | Spec.    |      |      |      |

|---------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|------|------|------|

| Signal  | Item                                                                                                                        | Symbol                      | Min.     | Тур. | Max. | Unit |

|         | Time that the MCU shall continue sending HS clock after the last associated Data Lane TCLK-POST has transitioned to LP mode |                             | 60+52xUI | -    | =    | ns   |

|         | Time to drive HS differential state after last payload clock bit of a HS transmission burst                                 | TCLK-TRAIL                  | 60       | -    | 2    | ns   |

|         | Time to drive LP-11 after HS burst                                                                                          | THS-EXIT                    | 100      | 1:-0 | -    | ns   |

| DSI_CP/ | Time to drive LP-00 to prepare for HS transmission                                                                          |                             | 38       |      | 95   | ns   |

| DSI_CN  | Time-out at Clock Lane Display Module to enable HS Termination                                                              | TCLK-TERM-EN                | -        | -    | 38   | ns   |

|         | Minimum lead HS-0 drive period before starting Clock                                                                        | TCLK-PREPARE<br>+ TCLK-ZERO | 300      | -    | £    | ns   |

|         | Time that the HS clock shall be driven prior to<br>any associated data Lane beginning the<br>transition from LP to HS mode  |                             | 8xUI     |      |      |      |

Clock Lanes High Speed Mode to/from Low Power Mode Timing

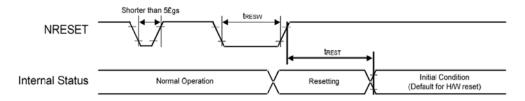

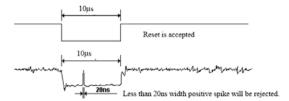

# 6. Reset timing

| Cumbal | Parameter                          | Related |      | Spec. |      | Note                                  | Unit  |

|--------|------------------------------------|---------|------|-------|------|---------------------------------------|-------|

| Symbol | Parameter                          | Pins    | Min. | Тур.  | Max. | Note                                  | Ullit |

| tRESW  | Reset low pulse width(1)           | NRESET  | 10   | -     | -    | -                                     | μs    |

| +DEST  | Deset complete time(2)             | -       | 15   | -     | -    | When reset applied during SLPIN mode  | ms    |

| tREST  | Reset complete time <sup>(2)</sup> | -       | 120  | -     | -    | When reset applied during SLPOUT mode | ms    |

#### Notes:

- 1. The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NVM (or similar device) to registers. This loading is done every time when there is HW reset cancel time (tREST) within 5 ms after a rising edge of NRESET.

- 2. Spike due to an electrostatic discharge on NRESET line does not cause irregular system reset according to the table below:

| NRESET Pulse         | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 10us     | Reset          |

| Between 5us and 10us | Reset starts   |

- 3. During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out -mode. The display remains the blank state in Sleep In -mode.) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection also applies during a valid reset pulse as shown below:

5. It is necessary to wait 15msec after releasing NRESET before sending commands. Also Sleep Out command cannot be sent for 120msec.

MODEL:VM05B4 VN Page: 18/21 Doc. No: **Preliminary**

# 7. Reliability Test

Environment test conditions are listed as following table.

| Items                            | Required Condition                 | Note |

|----------------------------------|------------------------------------|------|

| Temperature Humidity Bias (THB)  | Ta=40°C, 80%RH, 240hours           |      |

| High Temperature Operation (HTO) | Ts= 70°C , 240hours                |      |

| Low Temperature Operation (LTO)  | Ta= -20°ℂ , 240hours               |      |

| High Temperature Storage (HTS)   | Ta= 80°C , 240hours                |      |

| Low Temperature Storage (LTS)    | Ta= -30°C , 240hours               |      |

| Thermal Shock Test (TST)         | -20°C/30min, 60°C/30min, 100       |      |

|                                  | cycles                             |      |

| On/Off Test                      | On/10sec, Off/10sec, 30,000 cycles |      |

| ESD (ElectroStatic Discharge)    | Air Discharge: ± 6KV,              |      |

|                                  | 150pF(330Ω ) 10 times              |      |

Note 1: The TFT-LCD module will not sustain damage after being subjected to 100 cycles of rapid temperature change. A cycle of rapid temperature change consists of varying the temperature from -10 $^{\circ}$ C to 50 $^{\circ}$ C, and back again. Power is not applied during the test. After temperature cycling, the unit is placed in normal room ambient for at least 4 hours before power on.

MODEL:VM05B4 VN Page: 19/21 Doc. No: Preliminary

8. Shipping package (TBD)

MODEL:VM05B4 VN Page: 20/21 Doc. No: Preliminary

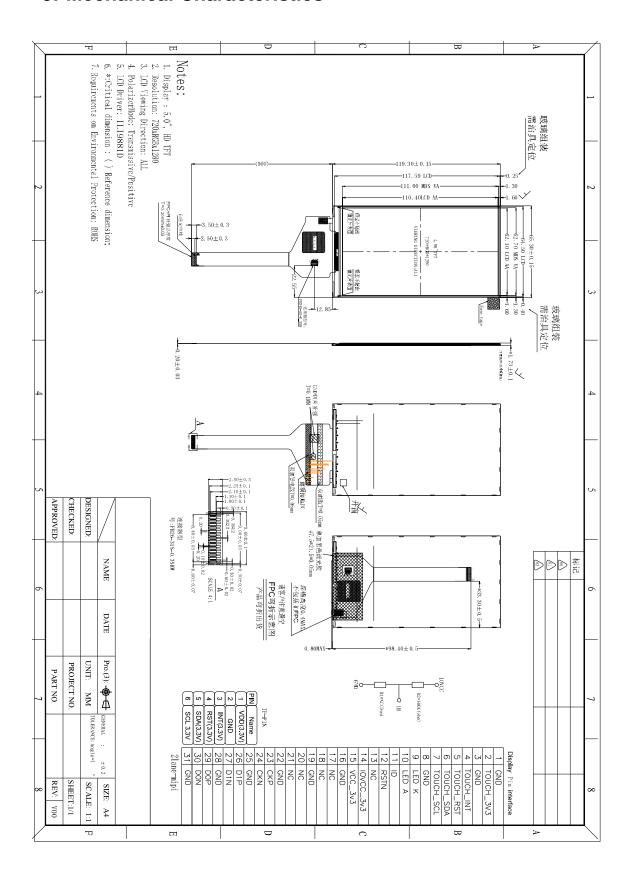

### 9. Mechanical Characteristics

MODEL:VM05B4 VN Page: 21/21 Doc. No: